軟件定義時間敏感網絡系統是在軟件定義網絡框架下融入了時間敏感網絡技術的綜合性網絡系統。該系統既具備軟件定義網絡的組網靈活性、協議無關轉發的高適應性、轉發控制分離的高效性與可控性,同時又有低延時、低抖動的時間敏感特性。該系統通過軟件流表與隊列映射的靈活定義,極大放寬了全網流規劃調度的難度,增強了TSN網絡的適用范圍和行業兼容能力。

時間敏感是業務的屬性,故在業務流交互過程中分組所經歷的所有處理環節都要滿足時間敏感特性才能夠真正保證業務的時間要求。TSN一定是一個完整的時間敏感網絡系統。

湖南新實是OpenTSN項目的忠實支持者、貢獻者與推動者,OpenTSN 1.0開源版本(github與gitee均有下載)受到廣大TSN研究者的熱捧。在該版本基礎上,湖南新實網絡與沈陽自動化所結合應用行業特性要求做了大量的修改與改進,共同研發了一套較為完整的軟件定義時間敏感網絡系統。

軟件定義時間敏感網絡系統主要包括:端節點、交換機和控制器。其中端節點可分為實時端節點和普通節點。時間敏感流路徑上所有交換機都支持TSN規范要求。控制器使用SDN控制器Floodlight,部署在普通電腦上。端節點和交換機都使用OpenBox-S4設備,該設備核心芯片是Zynq-7020,由雙核CPU+FGPA異構組成,采用FAST架構搭建網絡IO系統。通過軟件靈活配置可運行為端節點或交換機。

基于FAST架構的OpenBox-S4平臺

該系統的TSN功能全部由FPGA邏輯實現,包括時鐘同步和Qbv調度。其中PTP分組同步數據根據硬件流表控制轉發,確保同步分組雙向路徑對稱。所有分組數據均可在不同節點根據硬件流表映射不同優先級隊列和輸出端口,既可有效降低規劃沖突,又能方便路徑規劃。所有分組數據均根據硬件相應流表轉發,既可由軟件動態配置,也可從本地存儲空間加載規劃配置好的所有流表。全FPGA實現功能與靜態流表加載非常適合在車載等相對固定的環境使用,搭建CPU后則適合大規模網絡環境和動態變化的網絡環境下使用。不僅適應BE流的動態變化,TSN流也可以通過流表方式動態規劃和配置。

1.端節點

實時節點:實時節點CPU運行硬實時操作系統,包含PL側的實時驅動、實時網絡協議棧和實時應用,如rtping和rtudp等。FPGA加載支持TSN功能的硬件邏輯,支持與網絡中時間主節點同步,支持流表映射和規劃調度設置。

普通節點:普通節點運行普通操作系統,包含PL側普通驅動,使用系統標準協議棧功能,支持標準的SOCKET應用,如ping和iperf等。FPGA邏輯加載FAST標準5級流水線功能邏輯。

2.交換機

交換機運行普通操作系統,包含PL側普通驅動,使用系統標準協議棧功能,支持標準的SOCKET應用。安裝運行OVS虛擬交換機,移植開發OVS流表硬件卸載功能、南向OpenFlow協議擴展支持功能,主要包括對TSN相關參數的配置,如硬件流表配置、門控列表等。

3.控制器

安裝運行于普通電腦上,需要移植開發對TSN相關屬性配置的北向APP、北向REST API、控制器支撐模塊、OpenFlow協議擴展模塊等。如TSN同步使能、調度使能、TSN門控列表配置、協議無關流表配置等。

4.系統演示環境

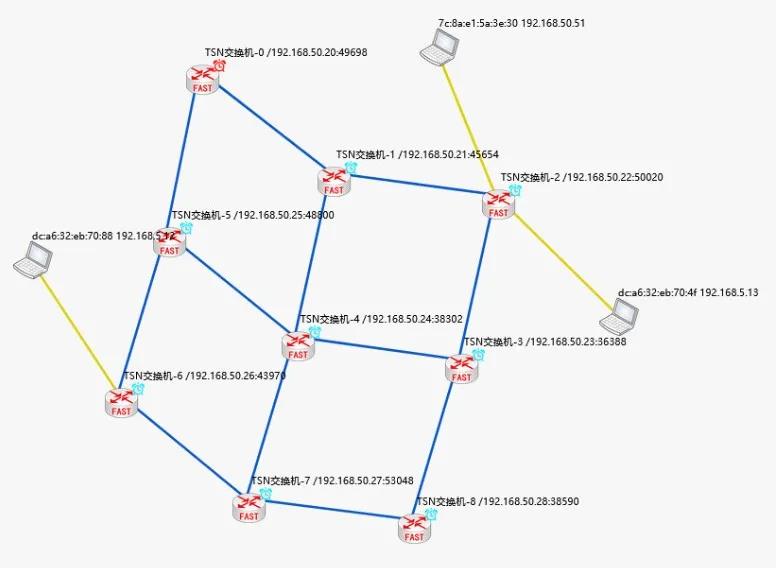

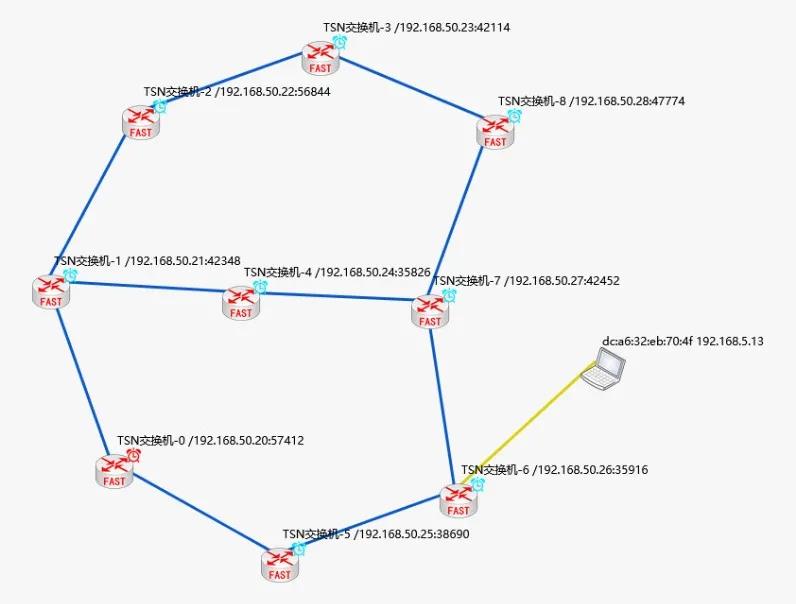

演示系統包含1個時鐘主節點(交換)、8個時鐘從節點(交換)、2個時鐘從節點(實時端)、1個數據采集監控節點和2個BE流普通節點。交換網絡連接為田字格,端節點數據流可通過軟件定義流表的方式做不同的路徑切換。

軟件定義時間敏感網絡演示系統

1.SDN控制器拓撲

2.SDN流表(端口輸出與TSN隊列映射)

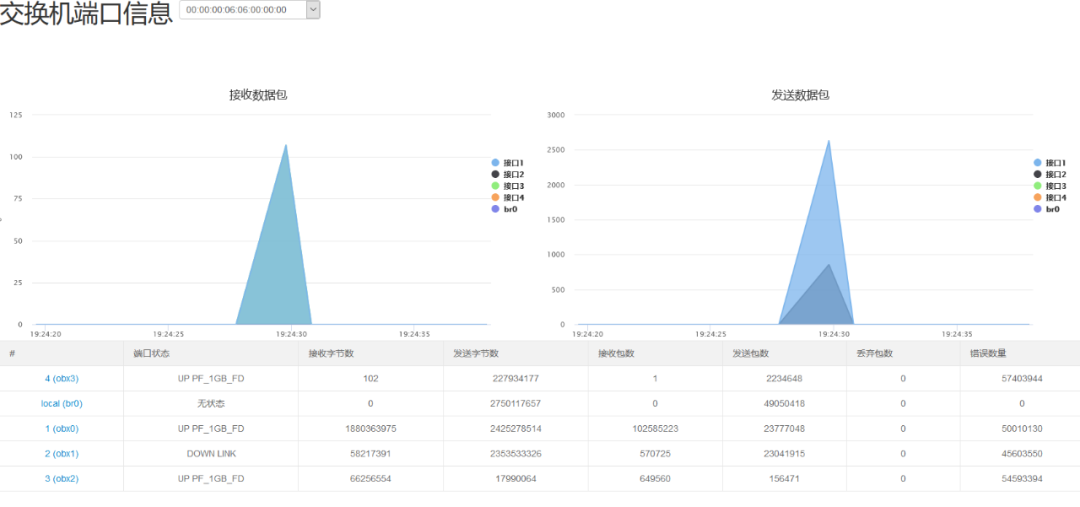

3.接口狀態與計數

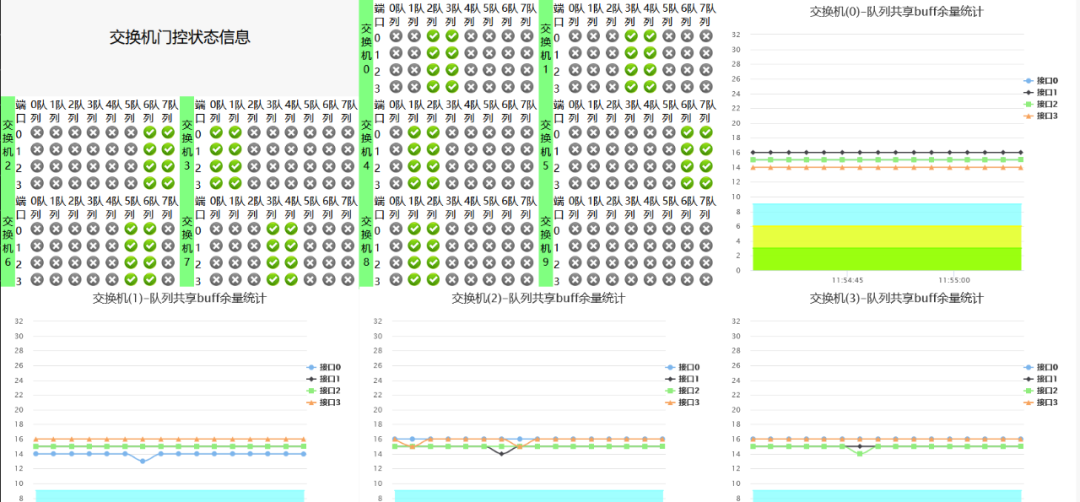

4.實時門控與BUFF統計

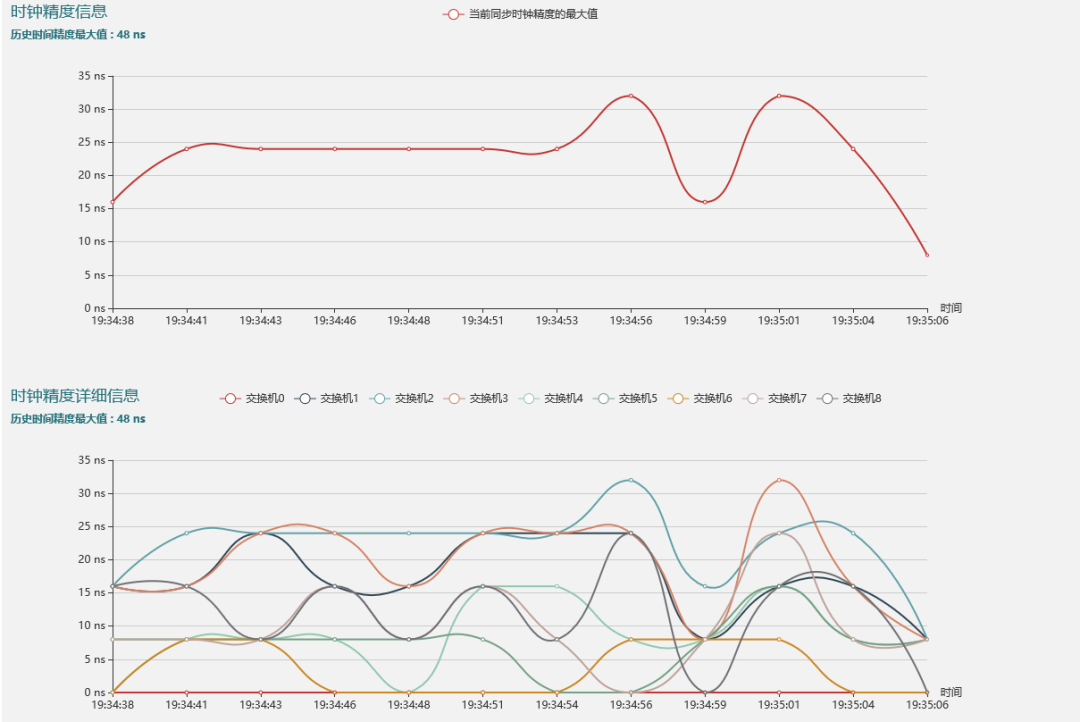

5.實時同步狀態

6.拓撲重組網

8.Qbv門控調度配置(靈活)

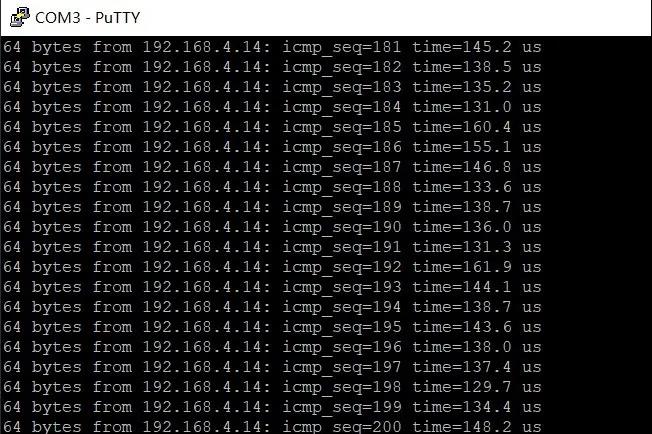

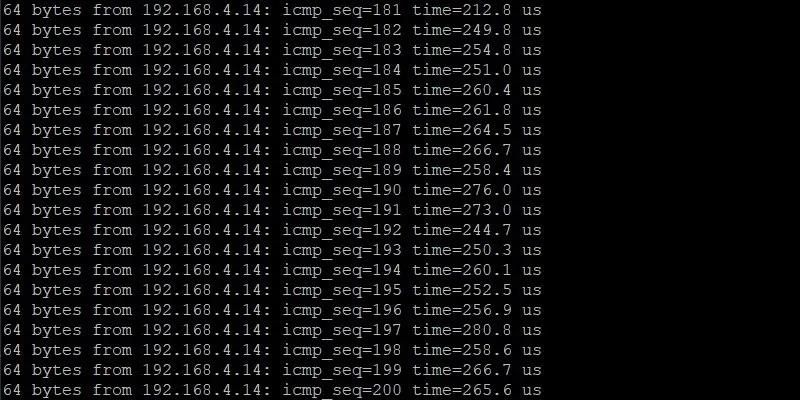

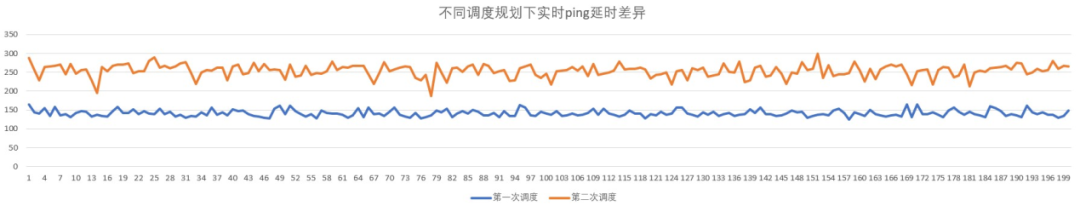

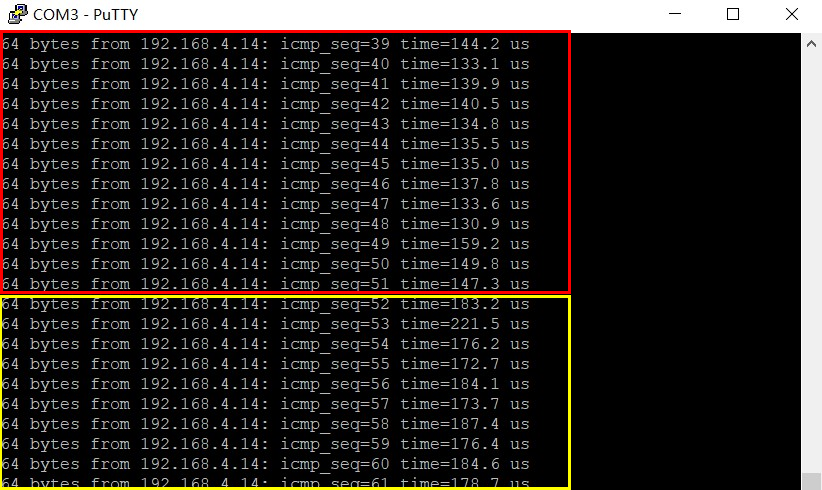

9.實時端系統實時ping

10.修改調度門控

11.新門控實時ping對比

12.路徑重規劃后實時ping對比(紅色A路徑,黃色B路徑)

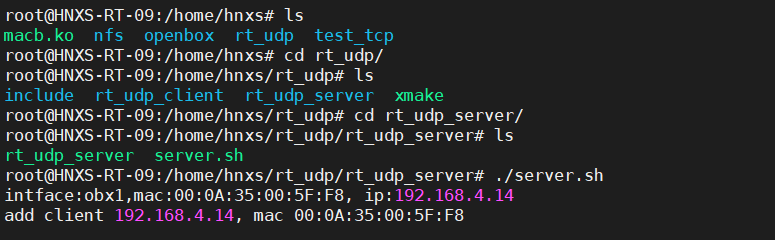

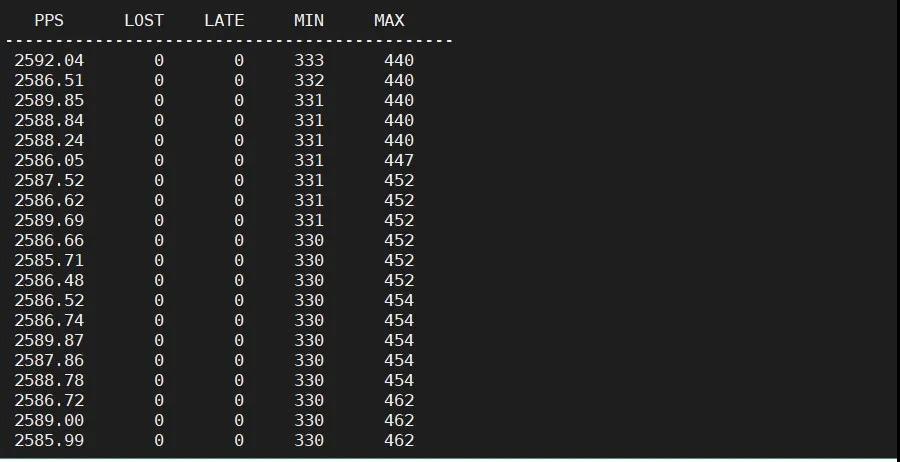

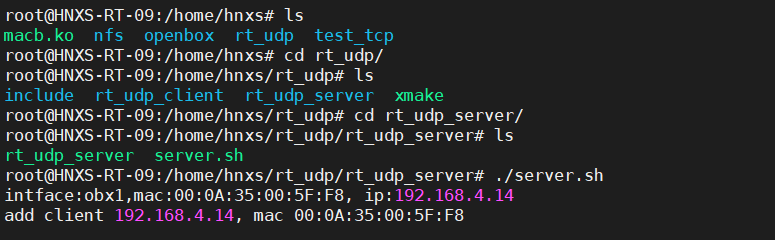

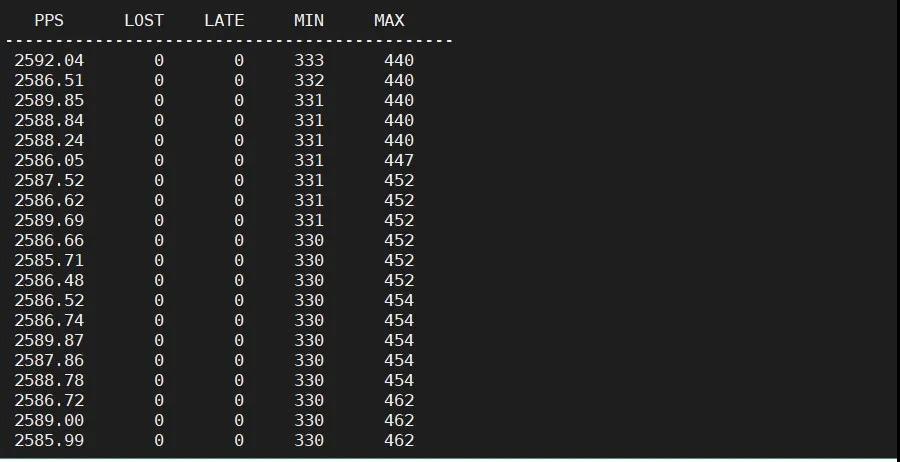

13.實時UDP通信測試

實時UDP服務端(接收并返回)

實時UDP發送、接收統計客戶端

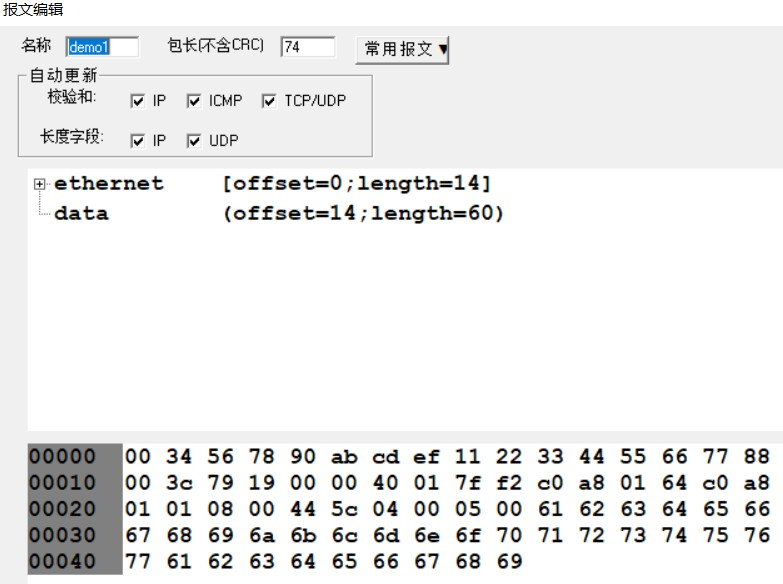

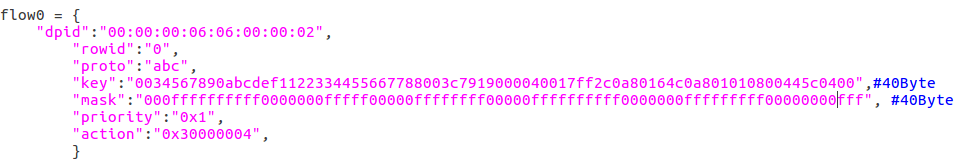

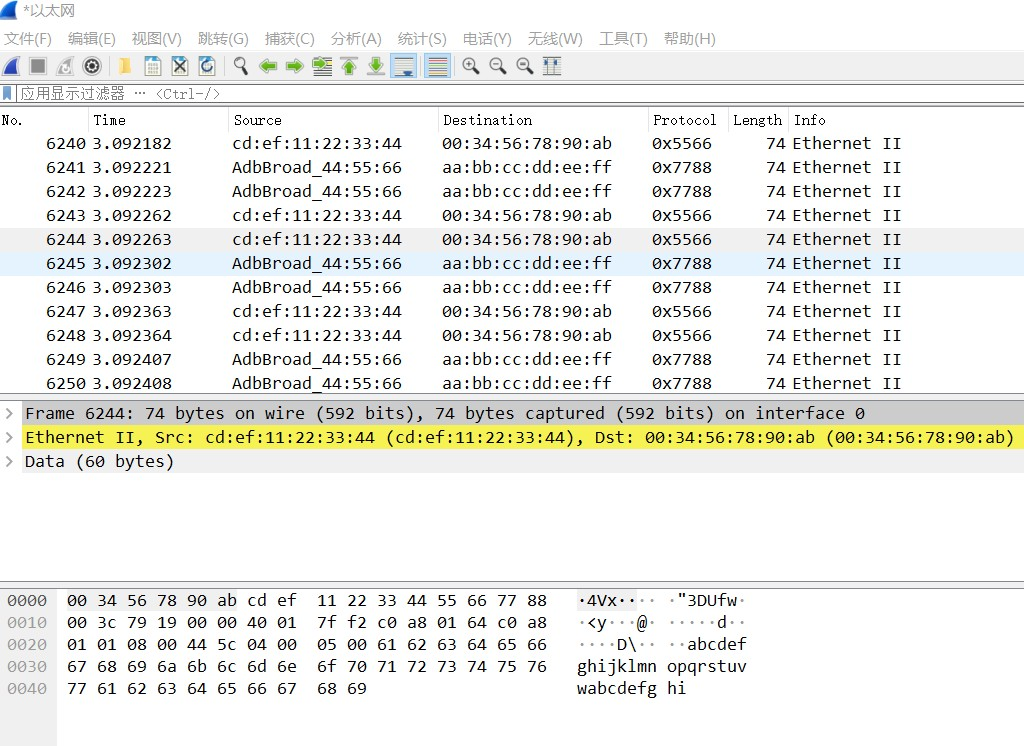

14.協議無關轉發(OT節點不移植協議)

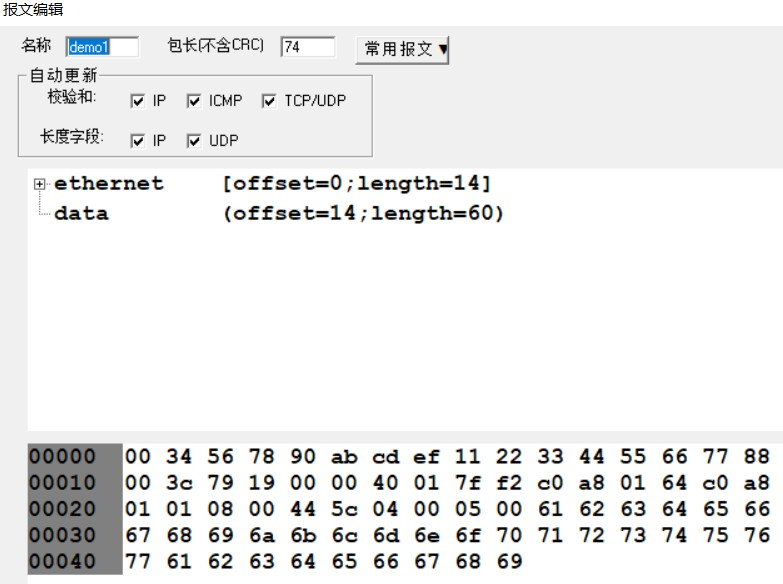

自由構包

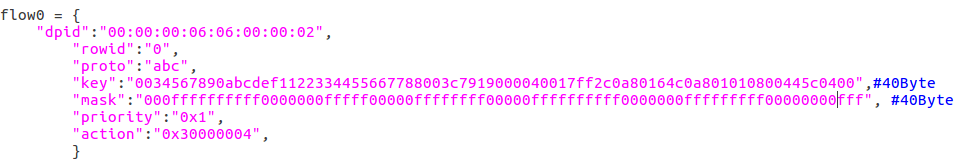

配置流表

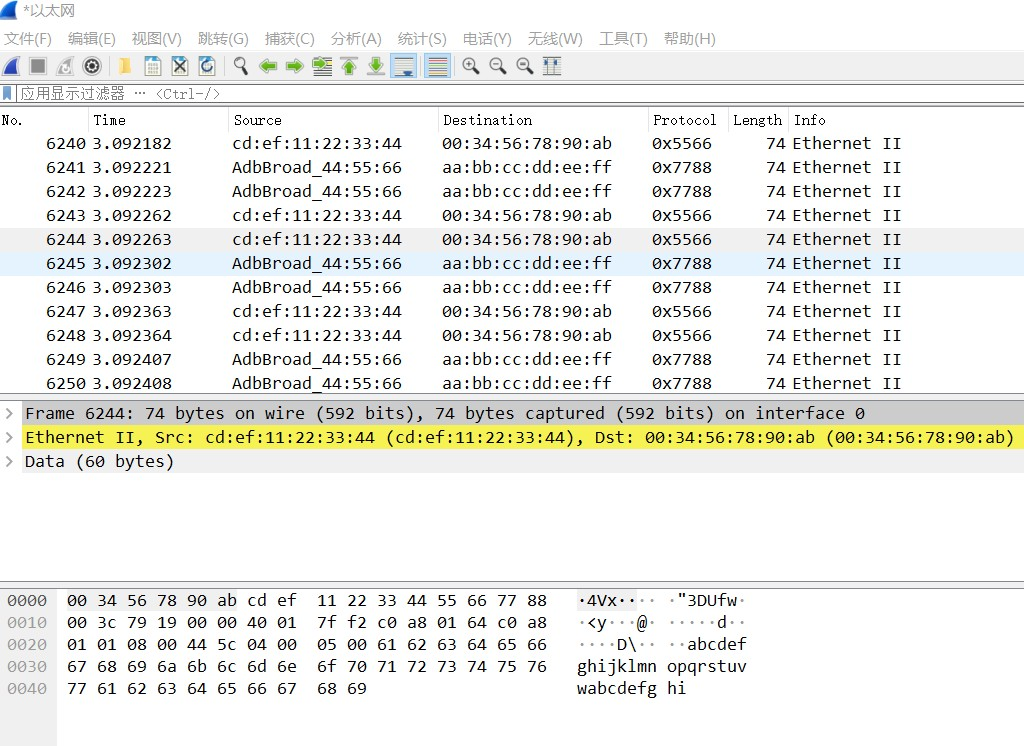

接收抓包

軟件定義時間敏感網絡系統是一個綜合性網絡系統,業務數據流經的每個層級和環節(應用、協議棧、驅動、系統調度、網卡、交換機等)都要求具備實時性,缺一不可。在不同的應用場景下或流特性要求不同的情況下,系統的解決方案不完全相同。比如端系統不一定要采用帶系統的環境,可以裸CPU運行,也可以使用PLC或純FPGA邏輯等方式。具體要看業務的運行環境和時間敏感需求,完全可以根據用戶要求實現各類定制需求。

上述驗證場景只是提供一了整套可能的使用方法,中間許多細節也并不完善,時間精度的控制及全網規劃調度也還需要進一步改進和優化。

歡迎大家多多交流溝通,多提寶貴意見,共同促進TSN網絡技術的普及發展。

關注FAST開源社區

FAST一一開源、開放、高速、高效、可編程、可定義!軟硬件協同并行處理。